# <u>2-1 TFT の分析評価及び SiGe-TFT 技術の開発(コア研究室)</u>

### テーマ概要

本テーマでは、Si より高キャリア移動度を有する SiGe からなる薄膜トランジスタ(TFT)技術、特に液晶ディスプレイへの応用を念頭においた技術の情報・動向の調査ならびに素子作製プロセスに関する探索研究より開始した。内外の技術動向、プロジェクト内でのテーマの選択と集中の方針により、平成 18 年 3 月末にコア研究室での SiGe-TFT プロセス技術に関する研究を継続しないとの判断を行なった。以後は、本プロジェクトの主テーマである ZnO-TFT および ZnO 透明電極技術の研究開発グループに寄与できる薄膜評価技術の開発を目的とした。特に外力の ZnO 薄膜の電気特性、機械特性への影響の検討とそれらに対する対策ならびに評価技術に的を絞って推進した。

### フェーズ

当初、ZnO-TFT と同様に重点テーマとして設定していたが、より ZnO-TFT 技術開発に注力したことにより、フェーズ の期間において、特段の研究成果は挙げられなかった。中間評価の指導もあり、SiGe-TFT 技術については探査研究に留め、継続し、ZnO-TFT 技術、次世代透明導電膜技術を補完する TFT の分析評価をテーマに盛り込み、フェーズ 以降の研究開発を行なうこととした。

### フェーズ

#### (1) SiGe-TFT 関連

フェーズ よりテーマリーダの山本直樹が参画し、テーマ人員 1 人体制で平成 17 年度は SiGe-TFT に関する技術情報調査およびプロセス技術探索の研究を行なった。

#### 【技術情報調查】

大型液晶ディスプレイの価格競争激化により従来の Si-TFT においても高速性能(高キャリア移動度)を追求するよりコスト低減技術の開発が主となってきた。これに連動して高移動度を期待した SiGe-TFT に関する研究・開発(特に液晶ディスプレイを想定して 500 以下に限定したプロセスで形成した TFT)は、本フェーズ期間にはほとんど報告されなくなった。この限定条件に最も近いプロセス条件で作製した SiGe-TFT に関する報告は、スタンフォード大学と香港大学からの 2 件がある。これらの報告では、スパッタ法で形成した SiGe 膜を 500 で長時間熱処理することにより、比較的粗大な結晶粒に成長させる固相成長法が用いられた。しかしながら、SiGe-TFT のキャリア移動度は約 50cm²/V·s 程度と現在の高性能液晶ディスプレイに用いられている低温多結晶シリコン TFT (LT-Si-TFT)に及ばない。これを凌駕する高速性能を実現するには、LT-Si-TFT と同様にパルスレーザアニールプロセスの適用が必要と考えられる。SiGe-TFTは材料自体の持つ高キャリア移動度を利用することにより、このような特別の熱処理を必要とせずに高性能の TFT を実現できることを期待されているが、技術報告調査範囲内では技術はそのレベルに達していないと言える。

# 【プロセス技術探索研究】

本テーマでは SiGe 膜の改善 (テーマ 2-2 において共同研究機関の名古屋大学大学院工学研究 料電子情報システム専攻の豊田浩孝教授が担当)とともに TFT 高速化に必要な素子構造実現のためのプロセス技術に関する探索研究を行なった。

TFT の高速化には 膜質改善、すなわち結晶粒の粗大化によるトランジスターチャンネル領域 のキャリア移動度向上とともに、 キャリアの移動距離、すなわちチャンネル長を短くすること が有効である。また ソース / ドレイン (S/D) の低抵抗化により、S/D に外部から加えられた

電圧を減少させることなくチャンネル領域に印加できる素子構造の実現が必要である。これらはすでにシリコン高集積回路(LSI)で用いられている。しかしいずれの方法も500 以上の高温熱処理を要し、液晶ディスプレイ用のTFTへの適用が困難であった。

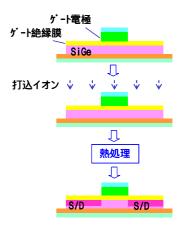

はゲート電極をマスクとしてボロンやリンなどの不純物イオンを SiGe 層にイオン打ち込みすることにより実現できる(図1)。すなわち S/D 域を規定するためのフォトマスクを用いることなくゲート電極パターン周囲に自己整合的に不純物をドーピングして S/Dを形成できる。この方法によれば、ゲート電極幅が短くなっても合わせ隙間のない S/D 域を形成きるため、高速化のための短チャンネル TFT の実現が容易にな

図1 S/D域への自己整合不純物 ドーピング工程流れ概略と素子断面図

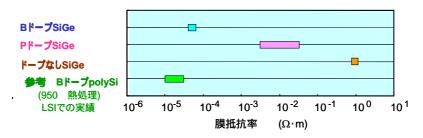

る。このように自己整合的にドーピングされた不純物は、イオン打ち込みされただけでは Si や Ge の元素が結晶構造の中で占める位置に置き換えられた状態にならないため、S/D は高抵抗である(不純物が電気的に活性化していない)。これらの元素位置をドーピング不純物で置き換えるには熱処理が必要である。LSI プロセスではこのために 900 ないし 950 の高温熱処理が加えられている。液晶ディスプレイ用 TFT ではそのような高温熱処理を施すことはできない。このため本研究では、以下の技術を開発することにより 500 以下でドーピング不純物の電気的活性化を可能とした。その技術のポイントは 400 ~500 でのイオン打ち込みと、それに続いた同温度域での 1~2 時間熱処理である。この技術により図 2 に示すように LSI プロセスで行なわれている 900 ~950 熱処理を施したボロンドープ Si と遜色の無い低抵抗(電気的活性化)を実現した。なお、同図に示したようにリン不純物の電気的活性化は不十分であり、さらなるプロセス技術の工夫が必要である。

図2 S/Dドーピング不純物の低温での低抵抗化(電気的活性化)

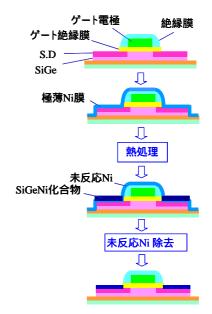

次に、先に述べた の S/D の低抵抗化技術について述べる。素子の高速化には で述べた不純物ドーピングした S/D をさらに低抵抗にすることが望まれる。その方法として LSI では、図 3 と同様のプロセス技術により不純物をドーピングした S/D 域表面のみに自己整合的に極薄の金属化合物を形成する技術が用いられている。この技術のポイントは、図のように極薄の Ni 膜を形成し、熱処理により Ni と Si や SiGe が直接接触した部分のみで選択的に反応させて、これらの金属化合物を形成する。そして未反応領域の Ni を所定のエッチング液を用いて除去して、金属化合物を S/D 領域の表面にのみ選択的に形成してその低抵抗化を図る。LSI プロセスでは図に示した熱処理は 450 ~500 で行なわれる。しかしこの熱処理で形成された金属化合物の抵抗は、あまり低くないため、図の最終工程、すなわち未反応 Ni を除去工程後にさらに 500 ~600 の熱処理が加えられる。しかしながら、液晶ディスプレイ用 TFT プロセスではこのような高温熱処

### 理を施すのは難しい。

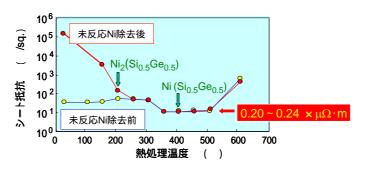

Si に Ge を混ぜることにより融点が低下すること はすでに知られている。これにともない他の金属と の反応開始温度も低下することを期待した。Ge を 20~50 atom%含有する SiGe を用いて、図3のプロ セスにより S/D 表面域に選択的(自己整合的)に Ni-Si-Ge 化合物を形成した。これらの SiGe 膜では Si 膜で報告されているものより 100 ~ 150 低温 の熱処理で金属化合物が形成されることがわかった。 図4にその例として 50atom%の Ge を含有する SiGe 膜と極薄 Ni 膜を反応させる熱処理温度とその とき生成した金属化合物層の抵抗の関係を示した。 図には未反応 Ni 除去前後の抵抗(シート抵抗)を 示しており、250 以上の熱処理で Ni はほぼ完全に 反応したことがわかる。また図には LSI で用いられ ている Ni-Si 化合物の 600 熱処理後の抵抗率を赤 枠で示した。SiGe では 300 ~ 350 の熱処理でこ

図3 自己整合SiGe金属化合物形成 工程流れ概略と素子断面図

れと同等の低抵抗が実現できることが明らかになった。すなわち、SiGe-TFT では図 3 に示した一回の熱処理(300 ~350 )で、最も低抵抗の金属化合物が形成でき、LSI における第 2 回目の熱処理工程を省くことができることがわかった。すなわち低温度形成とともに低コスト化が図ることができる。なお、同図には生成した化合物相を薄膜用 X 線回折装置で評価した結果を示した。300 ~350 熱処理で最も抵抗率が低いと考えられている Ni ( $Si_xGe_{1-x}$ )相が形成することを確認した。

以上に述べた S/D の自己整合ドーピング技術ならびに自己整合金属化合物形成技術の開発により素子構造から改善した高速 SiGe-TFT の見通しを得た。

図4 低温(200 ~500 )熱処理による 低抵抗極薄Ni-Si-Ge化合物形成

## (2) ZnO 薄膜評価技術関連

## 【ZnO 膜内の自発分極低減技術】

ZnO は wurtzite 結晶構造で  $P6_3mc$ 、 $C_{6v}^4$  結晶群に属しておりその非対称原子配置より力が加わると分極が生じる、いわゆる圧電効果発現材料である。製膜法により大小の差があるが薄膜には残留応力が存在する。このため ZnO 薄膜には  $50mC/cm^2$  程度の自発分極が存在すると言われ

ている。実際、高周波 (RF) スパッタ法で形成した wurtzite 結晶構造 ZnO 膜における各原子間 距離を求め、各種論文の実験データならびに理論解析を参照することにより、この膜にも  $45\text{mC/m}^2$  の自発分極が存在することがわかった。

TFT など ZnO 膜を用いたほとんどの電子デバイスでは膜面内方向に電子や正孔などのキャリアを移動させる。上述の自発分極は面内方向でなく膜の厚み方向に生じる。このためキャリア散乱などの影響は大きくないと考えられるが、分極により生じた固定電荷はゲート電圧のように作用して素子の電導特性を劣化させる可能性がある。このため自発分極を低減することが望まれる。

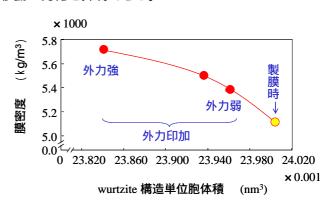

ZnO の結晶格子定数、亜鉛 酸素原子間距離と分極に関する多くの論文データの比較、整理より wurtzite 結晶構造単位胞体積と自発分極には相関があることを見出した。すなわち単位胞体積が小さくなると自発分極量が減少することがわかった。そして単位胞体積が小さくなることは当然、膜全体の密度が増大することと対応すると考えた。すなわち膜密度を向上させれば自発分極の少ない膜となり、分極電荷によるキャリア移動の劣化を抑制できる。

膜の自発分極を低減するために、膜の外部から力を加えて膜密度を向上する方法を開発した。膜に対して特定方向の力を加えることにより膜密度が向上することを見出した。図5に加えた外力の強さと膜密度ならびにwurtzite結晶構造単位胞体積の関係を示した。なお膜密度はX線干渉測定そして単位胞は極薄膜対応X線回折測定により求めた。図の中の強い外力を加えた膜では、その自発分極量は製膜状態の約半分の23mC/m²に低減されている。この実験では、

図5 外力による膜密度向上

外力の印加法として ZnO 膜上に一定応力を有する絶縁膜の厚さを変えて行なった。すなわち、外力強の場合は外力弱の場合より絶縁膜の厚さを 2 倍にした。この実験からわかるように、TFT などの電子デバイスでは、ZnO 膜上に形成するゲート絶縁膜やゲート電極、さらにはその上に形成する各種層の内部応力を調整することにより、自発分極による電導特性の劣化の少ない素子を実現できることがわかる。すなわち、高性能デバイスを得るには各層の応力設計が重要であり、逆の方向の力が ZnO 膜に加わるような設計をすると、高性能デバイスを得るのが難しくなると考えられる。なお、図 5 は高密度の膜を製膜できる技術の開発が、高品質 ZnO 電子デバイスを得るために必要であることを示している。

## 【極薄膜の機械定数非破壊評価技術の開発】

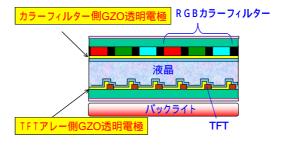

図6 液晶ディスプレイ断面概略図

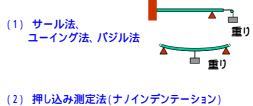

ヤング率は図7に示すように、古来より多くの評価技術が用いられてきた。それらの基本的な 考え方はヤング率を以下の関係より求める。

ヤング率 = (外部から加えた力/物体の断面積)/(伸びた量/元の長さ)

図7 従来のヤング率測定法

これらの測定法の中で、薄膜のヤング率測定に最も広く用いられているのは(2)の押し込み測定法である。この方法では、圧子(針)を膜に押し込んだとき膜に生じる圧痕の形状と圧子に加えた荷重の関係よりヤング率を求める。したがって、あまり薄い膜の場合は圧子先端が膜深く侵入して基板界面近傍に到達する。このような状況になると正確なヤング率を得ることができない。このため、適用できるのは約 1μm 厚程度までで、それより薄い膜にこの方法を用いるのは適切でない。またこの方法は針の先端部程度の局所部の値しか得られない欠点がある。

そこで液晶ディスプレイの透明電極のように、膜厚が上述より約一桁薄い膜の評価法の開発を めざして検討を行なった。上に示したヤング率を求める関係式をさらに進めると次の式に到達す る。

ヤング率 = 応力(σ)/歪(ε)

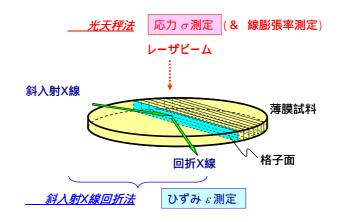

したがって膜の応力と歪を測定すればヤング率が求まることになる。論文調査したところ、こ の式を用いてヤング率を求めた報告は見つからなかった。そこで、以下のような極薄膜に適用で きるヤング率測定法を開発した。その要点を図8に示した。

図8 本開発の非破壊極薄膜ヤング率測定法

基板上に GZO などの膜を形成したとき、その残留応力により基板が曲がる。試料にレーザービームを照射して基板の曲がり量を測定することにより、膜の持つ残留応力  $(\sigma)$  を測定する(光天秤法)。このとき測定される応力は膜面内方向の成分である。この応力が存在すると、必ず膜の面内方向に歪  $(\epsilon)$  が存在する。この歪を膜の全反射角に近い極低角度から X 線を照射して、膜面内方向の結晶格子面により回折した X 線を測定することにより、面内方向の歪を求めることができる(斜入射 X 線回折法)。これらの測定値から上に示した式を用いて、薄膜のヤング率を測定することができる。この方法はレーザと X 線の光ビームを用いるため、試料のあるがままの状態を非破壊で測定できる特長を有している。Z のなどの結晶膜のヤング率は結晶方位により異なるのが一般的である。先に述べた押し込み法では指定された面方位のヤング率を求めることはできなかった。本開発の測定法では面方位ごとのヤング率を求めることができる。さらに本方法では、少し工夫するだけで積層膜のヤング率を求めることができるなど、従来にない特長を有している。また次に述べる GZO 極薄膜の測定より 10nm 程度の超極薄膜のヤング率も測定できる優れた能力を有していることが確認された。

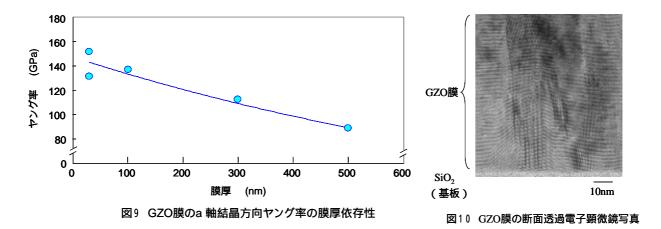

本方法を GZO 膜に応用した。シリコンウエハを熱酸化してその表面にシリコン酸化膜を形成して基板とした。その上に 30nm~500nm の厚さの異なる GZO 膜を形成してそれらのヤング率を求めた。用いた GZO 膜は研究テーマ 3-1 の研究グループが開発した反応性プラズマ蒸着装置 (RPD) 装置により形成した。この膜は膜厚方向に wurtzite 結晶構造の c 軸が配向しており、

膜面内方向に a 軸がある。この a 軸方向のヤング率を測定して図9に示した。ヤング率は膜厚とともに減少することがわかった。ヤング率は材料の硬さのバロメーターでもある。したがって膜が厚くなるとともに軟らかくなることがわかった。この結果は、結晶構造を透過電子顕微鏡(TEM)により観察した GZO 膜の断面像の図 10 と対応している。GZO 膜の断面像には白と黒の縞模様が見られる。これらは wrutzite 結晶構造において、交互に積層した亜鉛の原子層と酸素の原子層に対応している。基板界面近傍ではこの積み重なり方向にバラツキがあり、原子層が交互に積層する方向(c 軸方向)が結晶粒ごとに異なっている。また各原子層は、結晶粒界で途切れているのがわかる。このような不連続部では外部から力が加わったときに積層原子面内で原子が移動できなくなる。すなわち膜は硬くなる。一方、界面から離れた領域(厚膜領域)では、これら原子層面はいずれの結晶粒においても基板面に垂直方向に規則正しく積層されている。そして厚膜領域では、各結晶粒界で途切れずに連続しているのがわかる。このような構造を有する場合は、外力が加わっても各結晶粒間で原子の移動が可能になる。すなわち膜は軟らかくなる。このような膜厚とともに原子層の積層方向が整ってくるために図9に示したように、膜厚とともにヤング率が減少することがわかる。

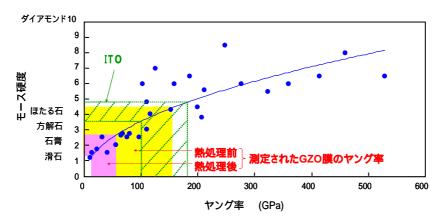

図11 各種材料の硬さとヤング率の関係

物質の硬さはモース硬度により表示されることが多い。同じ材料についてモース硬度とヤング率を論じた文献を探し、種々の材料の両物性値の関係を求めた。図 11 中の青ドットは論文調査により得た各種材料のデータである。ヤング率とモース硬度は良い相関を持つことがわかる。同図には、論文より得た ITO 透明導電膜の値も示してある。そして今回開発したヤング率測定法で求めた種々の膜厚の GZO 膜の値を、黄色の領域で示した。この図より、RPD で製膜した GZO膜は ITO より軟らかい、すなわち ITO より機械的衝撃に対して耐性が高いことが明らかになった。なお GZO 膜は 500 の熱処理により桃色で示した領域までヤング率が減少、すなわち滑石と同程度まで軟らかくなることが明らかになった。

今回開発したヤング率評測定技術は工夫をすることにより線膨張率、ならびに膜の下地に対する接着力を非破壊で測定することができる。線膨張率は試料を加熱しながら測定することにより、接着力は複数試料の測定値を用いて導出する。RPD で製膜した GZO 膜の線膨張率はヤング率と同様に、膜厚とともに変化した。例えば、GZO 膜の線膨張率は 30nm 厚における  $4.8 \times 10^{-6}$  から 500nm の  $8.4 \times 10^{-5}$  まで増大した。この結果は、図 9 のヤング率や図 10 の TEM 観察像と良い対応を示している。薄い膜厚(界面近傍)では、GZO 膜は硬い(ヤング率が大きい)ため伸び難いが、厚膜(基板界面から離れた領域)では、軟らかく(ヤング率が小さい)なるため伸びやすく

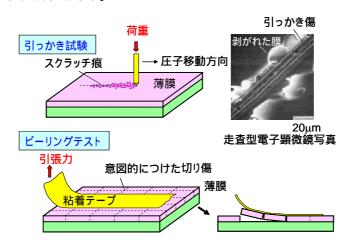

なる。接着力は RPD により SiO2 基板 (Si ウエ八を熱酸化)上に形成した GZO 膜について評価した。熱処理前の接着力は 1.3GPa であったものが、500 熱処理後は 1.0GPa まで減少することがわかった。これらの接着力は非常に強く、GZO 膜を液晶ディスプレイの ITO 透明電極に置き換えても、その製造過程、あるいは稼働中に剥離などの問題を発生することは無いと思われる。なお、膜の剥がれは LSI、各種記憶ディスク媒体、液晶ディスプレイあるいは太陽電池など、薄膜を用いるほとんどのデバイスの製造工程で必ず悩まされるトラブルである。このため古来より多くの接着力評価法が提案されてきたが、現在最も広く用いられているのは図 12 に示した引っかき試験とピーリングテストである。

図12 代表的な接着力評価法

前者は圧子に荷重をかけながら膜上を移動させ、図の写真のように膜が剥がれた荷重をモニターとして接着力を相対的に評価する。後者のピーリングテストは、膜に粘着テープを貼り付け、そのテープを引っ張ったときの剥がれの有無で接着力を評価する。いずれの場合も、接着力のみを評価することができない。また接着力の絶対値を求めることができない。すなわち評価結果には、接着力以外の要因が重畳する欠点がある。例えば引っかき試験の場合は圧子の材質や先端の形状、披検膜の硬さ、滑りやすさ、そしてピーリングテストではテープの粘着材の膜に対する接着性やテープの伸びやすさなどが測定値に重畳する。またいずれも膜を破壊して評価する方法であり、同じ試料について繰り返し測定することはできない。

本研究で開発した接着力測定技術は膜のあるがままの状態を破壊することなく繰り返し測定でき、かつ接着力のみをその絶対値で測定することができるなど、従来にない画期的な特長を有する。この特長により未解明な部分が多かった、接着力の材料科学の見地から研究が進むとともに、膜材料と下地材料の接着力に関するデータベース蓄積により各種デバイスプロセスの開発において剥離予防を可能とし、製造コストの低減やデバイス稼働中のトラブルを予防する技術の開発に貢献できると思われる。

### 今後の展開

フェーズ では、経済産業省の「希少金属代替材料開発プロジェクト」の中の『透明電極向け ITO 代替材料開発』のテーマで 3-1 研究グループとともに液晶大型ディスプレイ向け製品実用化 技術を開発することになった。本研究テーマのリーダーも同プロジェクトに参画し、今回開発した機械定数評価技術を液晶ディスプレイの材料・プロセス開発の中で応用し、その有用性を実証していく。また、この応用を通してヤング率、線膨張係数そして接着力のデータベースを構築し、

薄膜材料および界面物理など学問的分野に寄与していく。

開発した評価技術は分析装置化することが可能なため、地元高知県を中心とした企業とともに 製品化の可能性を探り、実用化に努力する。

# その他

本テーマで開発した極薄膜機械定数非破壊評価技術は、すでに磁気ディスク、LSI および薄膜コーティングメーカーなど各種研究・開発機関から問い合わせがある。従来にない特長を有しているため期待が高いことを実感しており、分析装置あるいは評価技術として種々の産業分野に積極的にアプローチしていきたい。